借助Aprisa,将您的HPC设计创新更快地推向市场

为高性能计算(HPC)应用设计集成电路(ic)在整个流程中都面临着严峻的挑战。芯片制造商需要平衡性能和功耗,满足紧迫的设计时间表,并管理工程资源。正确的数字实现工具和方法可以帮助解决HPC设计中的棘手问题,包括放置和时钟树的挑战。

您可以在下载新的技术论文“用于高性能计算设计的布局和CTS技术”时了解更多细节,包括真实的客户示例。

高性能计算芯片的放置和时钟树解决方案

放置和时钟树合成是高性能计算芯片物理设计中的关键步骤,它们带来了一些挑战,包括拥塞、时序关闭、功耗和热考虑以及设计规则约束。

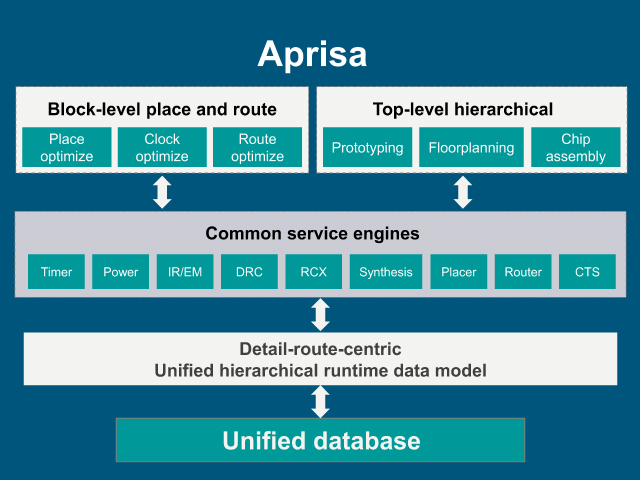

为了解决高性能计算应用中集成电路的所有挑战,西门子EDA提供了Aprisa,这是一种用于分层和块级设计的现代物理设计实开云体育平台登录现解决方案(图1)。Aprisa以详细路线为中心的架构减少了设计关闭的时间,其统一的数据模型在整个流程中共享,为任何引擎和位置和路线流程中的任何步骤提供真实的路线信息和基础。这允许在不同引擎间实现一致的计时和drc。Aprisa的内在智能确保设计人员将看到与签名工具的良好相关性,并减少eco的数量。

Aprisa架构使其能够利用详细路由的先进知识来优化放置,从而最大限度地减少了对设计人员手动指导的需求。在Aprisa中,您可以减少或完全消除放置指南,从而快速实现最佳放置,而无需依赖广泛的工程专业知识和全流程预运行。这种对时间、面积、功率和拥塞的早期洞察直接转化为节省时间和成本,特别是随着当今ic的复杂性和尺寸而增加的设计周期。

通过更好的分析来权衡设计

在高级节点上进行设计时,您需要仔细权衡节省电力的好处与额外金属层的额外成本。每增加一层金属层都会大大增加制造成本,通常会超过数百万美元。

通过Aprisa对性能、功率和面积(PPA)指标的早期洞察,您可以在流程的早期快速评估优化性能、功率和成本的选项。在保持上市时间目标的同时研究指标的机会,可以让您对影响底线的权衡做出明智的决定。

用于高性能计算芯片的时钟树

时钟树合成(Clock tree synthesis, CTS)是高性能计算(HPC)设计中的另一个主要挑战,它是物理设计过程中的关键步骤,因为它决定了设计的最终时间。CTS包括将时钟源路由到所有的接收器,包括寄存器、锁存器、时钟门和宏时钟引脚。低质量的CTS可能导致时序差、高功耗和信号完整性差。

CTS的质量受到三个主要因素的影响:时钟倾斜、插入延迟和缓冲。Aprisa支持有用的倾斜,从定位开始,一直持续到路线优化,因此可以满足具有挑战性的频率目标。Aprisa CTS技术的一个优势是,在放置优化过程中产生的推拉偏移在时钟树实现过程中实现。

由于Aprisa从布局优化阶段开始就了解CTS,因此它可以生成最优的时钟树并降低时钟功耗。

在后CTS和路由优化期间,Aprisa将恢复在CTS期间产生的拥塞,而不会影响时间。使用传统工具,设计师必须反复优化布局以减少拥堵。Aprisa还可以在后期应用有用的倾斜,以进一步改善时序并实现出色的相关性。

克服所有HPC设计挑战

Aprisa使用易于部署的开箱即用的参考流解决了高级节点上HPC设计的所有实现挑战。具有内在智能的Aprisa提供了业界领先的相关签名工具,同时提供了减少ECO迭代次数的技术。它通过高质量的时钟树、布局和专利路由技术确保所有PPA指标在HPC设计实施中得到仔细平衡,从而减少了组装过程中模块和顶层之间的时间关闭摩擦。

借助正确的位置和路径工具,您可以以更少的工程和计算资源,更快地将HPC设计创新推向市场。

在我们的白皮书中了解更多信息:高性能计算设计的布局和CTS技术.