AI/ML加速器教程:使用HLS |虚拟研讨会的c级设计与验证

在当今的ASIC和FPGA设计中,弹射HLS(高级合成)和c级设计和验证将整个项目的开发时间缩短了一半或更多。它被用于为5G和通信、图像和视频处理、汽车和AI/ML等多个应用创建生产质量的HW加速器,速度比手工编码的RTL快得多,具有相同的功率、性能和面积。然而,许多刚接触HLS的人对于如何利用在抽象中提升的生产力优势,并且仍然拥有他们使用当前方法所拥有的验证封闭性和信心有疑问。

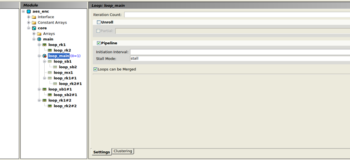

本次技术研讨会将是基于AMBA axis的子系统中AI/ML加速器设计的案例研究。它将逐步从算法到基于c的设计和系统级性能验证,HW/SW集成,然后通过RTL覆盖封闭展示工具和方法进行全面验证。

为了提供高质量的技术内容和更多的个人互动,我们将研讨会分为2天左右。每天3小时;第一天更侧重于设计,第二天更侧重于验证。除了开源示例和免费的按需培训之外,我们还增加了互动分组会议,与专家的现场问答,您可以在研讨会结束后自己尝试。请在下面注册,保存您的位置,我们期待着在那天看到您的现场。

日期:6月22日和24日,9:00 -12:30 pm太平洋时间

欧洲的日期:欧洲中部时间6月29日和7月1日15:00-18:30