FPGA和专用集成电路的开发依赖于概括性和可读性

质量和开发时间是现场可编程门阵列(FPGA)和专用集成电路(ASIC)设备开发人员的关键参数,但在大多数项目中都有显著的改进潜力。因此,评估如何开发这种改进潜力是至关重要的。

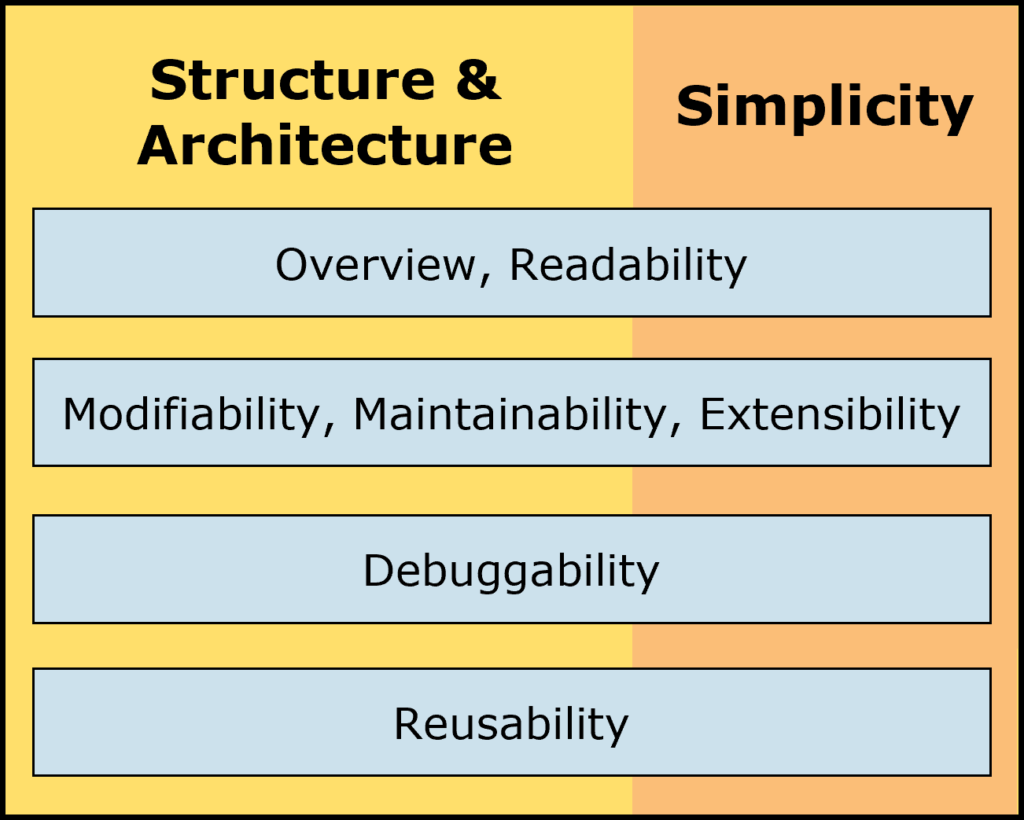

概述和可读性是所有改进参数的关键

上图是对提高质量和效率的基本参数的简要总结。这些都是适合FPGA和ASIC开发的关键。但是,如果您更深入地研究每个参数,很明显,概览和可读性要么是该参数的重要部分,要么是其要求。

可读性主要是指理解实际代码的容易程度,当然还有代码的接口。概览指的是理解总体情况的容易程度,无论是两段代码在底层如何交互,还是顶级模块如何协同工作。因此,可读性和概览是部分重叠的。因此,高可读性产生更好的概述,而更好的概述产生高可读性。

在FPGA和ASIC开发过程中,请记住可修改性

可修改性、可维护性和可扩展性也略有重叠。可修改性和可维护性是指对设计或测试平台进行安全更改的容易程度。术语可修改性适用于在开发过程中适应和更改功能。可维护性描述了由于bug和后来的改进而产生的更改。可修改性在规范不稳定或需要架构更改时特别有用,例如,为了允许更高的频率或吞吐量。可扩展性指的是扩展功能,而不仅仅是更改它,因此,这通常是一个更复杂的过程。

在所有FPGA和ASIC开发参数中,概述和可读性是至关重要的。如果没有良好的概览和可读性,任何重要的更改都可能是危险和耗时的。但是,很难看到重要代码或块更改的所有结果。解决一个问题会导致另一个问题,这种情况并不少见。添加新功能时也是如此——即使新功能非常简单。

通过设计这些参数,大多数公司可以在典型项目中实现20%到50%的效率提高。对于棘手的项目和复杂的模块,有可能提高200%到300%的效率。然而,大多数公司似乎并没有在开发过程中充分应用这一点。这可能是由于缺乏意识和对后果的误解。

好的设计和可调试性是相辅相成的

根据2020年威尔逊研究集团功能验证研究,调试占FPGA和ASIC开发工作总量的25%左右,这可能远远超过大多数人的意识,因此没有得到应有的重视。

这里有两个主要方面很重要。首先,也是最明显的,我们需要提高调试效率。这可以通过改进测试台架的结构和概述以及测试用例的可读性和可控性来实现。由结构良好的测试平台和测试用例生成的模拟副本的质量和可读性是不可或缺的。

其次,可能不太明显的是,一个好的FPGA设计或ASIC设计可以更容易地找到错误的根本原因——甚至更好——从一开始就大大减少了错误的数量。同样,这也是一个概览性和可读性的问题。

可重用性是理想的

术语可重用性可以在许多方面应用——用于设计和验证。即插即用重用是最有效的,但实现起来具有挑战性,因为它100%依赖于无需修改的直接重用。与之相反的是“默认”重用,即基于遗留设计或测试平台制作新的变体。默认重用的问题在于它依赖于未准备好的修改,因此容易出错且耗时。

在大多数情况下,最好的方法是为修改和扩展而设计。通过这样做,您可以极大地简化和保护以前的设计和测试工作台的重用。反对这种方法的最常见的论点是基于这样一个假设:它太耗时了。然而,如前所述,这是不正确的。为修改和扩展而设计可能会在前期花费更多的时间,但会显著减少FPGA和ASIC的开发时间,并带来更好的质量。同样,概览性和可读性对于效率和质量都至关重要。所以,问题是:“我们如何才能实现上面提到的所有好处?”答案很简单,而且不用花钱。

答案就在架构中

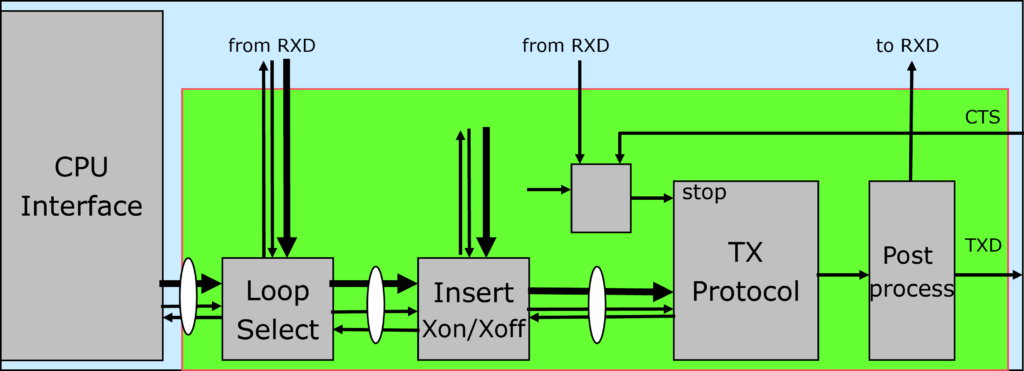

在开发设计或测试台中,体系结构始终是最关键的方面。大多数人都知道这一点,所以任何设计的顶层通常都有良好的架构。然而,不幸的是,对体系结构的同样关注并没有给予测试工作台。此外,在设计和测试台架开发中经常严重缺乏称为微体系结构的低层体系结构。虽然最初用于微处理器的底层架构,但术语微架构也适用于任何复杂模块的底层架构。通用异步收发器(UART) Tx模块的微体系结构如图2所示。

对于任何复杂的设计或测试平台,都需要良好的微架构来获得高质量的概述。微架构越好,就越容易阅读和理解底层代码。

许多开发人员认为“好的架构”等同于“结构良好的设计”。这是否准确完全取决于您如何开发架构。在所有层面上,概览和可读性应该是最高优先级;否则,在我看来,你将得不到好的架构。

架构是关于分层设计或测试工作台,然后“分而治之”。在软件开云体育官网入口中,人们还经常谈论“最大内聚和最小耦合”。这在设计和验证方面都有很多优势。

优秀架构的例子

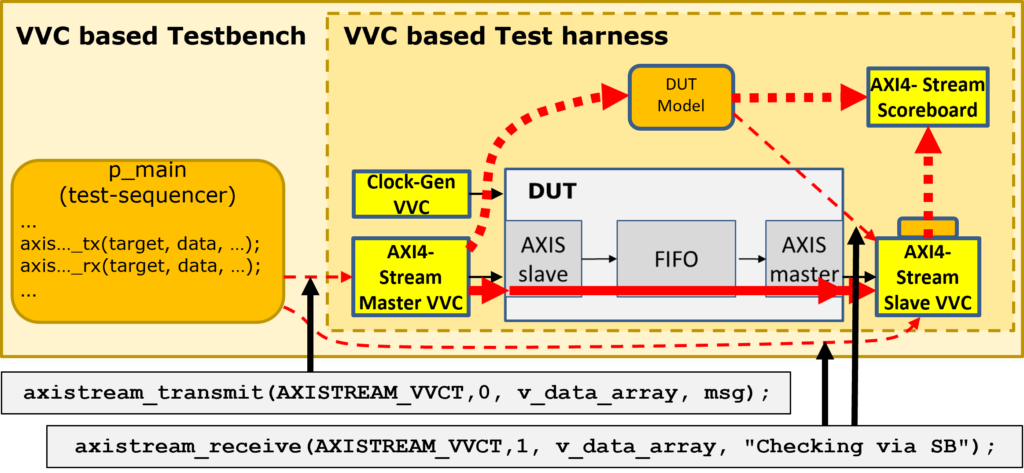

良好的设计架构对于质量和效率、功耗、时序关闭和许多其他关键设计参数至关重要。例如,请从2021年10月开始阅读我的博客“如何避免现场可编程门阵列和特定应用集成电路项目的延误“试验台架构几乎和设计架构一样重要,因为效率和质量在很大程度上都是如此。事实上,对于复杂设计的验证,试验台体系结构可以提供完整试验台的优秀概述,包括所有单独的验证组件以及它们之间的乐高式连接。图3说明了这一点。你可以在我的文章“UVVM - VHDL验证方法,用于更快更好的FPGA和ASIC验证”。

图3中没有说明的一个重要细节是,单个测试排序器可以控制所有DUT(被测设备)接口。该方法的这一独特特性产生了最好的概览和可读性。

FPGA和ASIC开发的效率和质量

概览和可读性、良好的体系结构、简单性以及图1所示的成功项目的所有其他元素对实现来说都不是太大的挑战。然而,让所有项目经理和相关职能部门接受它们的重要性可能是一个挑战。例如,在开始编码之前允许足够的准备时间可能会与传统的项目进度产生冲突。

优先考虑概览和可读性可能会要求大多数公司重新评估他们的整个开发方法,这可能是一个痛苦的过程。然而,另一种选择将会更糟糕。

类创建测试台的详细信息Xcelerator学院的通用VHDL验证方法(UVVM).

作者简介

埃斯Tallaksen他是UVVM的作者和架构师,也是Bitvis(2012-2019)和EmLogic(成立于2021年1月)的创始人。他对方法论的培养、实用效率和质量改进有着浓厚的兴趣,并在全球会议上进行了多次演讲,得到了很好的反馈。他还在全球范围内提供FPGA设计和验证课程。

关于EmLogic

EmLogic是一家软件和开云体育官网入口技术合作伙伴,也是领先的北欧现场可编程门阵列(FPGA)和嵌入式系统设计中心。架构思维对EmLogic的开发方法至关重要,因为质量和效率对客户至关重要。有关EmLogic, UVVM和我们课程的更多信息,请访问其网站.

构建解决方案的合作伙伴

开云体育官网入口软件和技术合作伙伴使用西门子Xce开云体育平台登录lerator产品组合及其灵活的开放生态系统构建技术,以补充全面的数字孪生体,并为我们的共同客户提供定制化解决方案。这些合作伙伴通常开发、销售、支持和推广与西门子产品互操作的硬件和软件解决方案,并确保基础设施的兼容性。开云体育官网入口开云体育KENO快乐彩开云体育平台登录寻找合作伙伴来帮助您构建数字化解决方案.